## HIGH RELIABILITY 32-BIT RISC-V PROCESSOR CORE

|                                                               | 5                                             |                                                                  |                                               |  |

|---------------------------------------------------------------|-----------------------------------------------|------------------------------------------------------------------|-----------------------------------------------|--|

|                                                               | Description                                   |                                                                  |                                               |  |

| CC-RV32HR-C                                                   | High Reliability 32-bit RISC-V Processor Core |                                                                  |                                               |  |

| Category                                                      | Туре                                          |                                                                  | Status                                        |  |

| RISC-V Cores                                                  | RISC-V                                        |                                                                  | Under Validation                              |  |

| Deliverables                                                  |                                               |                                                                  |                                               |  |

| ♦ RTL code                                                    | <ul><li>Testbence</li></ul>                   |                                                                  | ch                                            |  |

| <ul><li>User manual</li></ul>                                 | ◆ SDK/IDE                                     |                                                                  |                                               |  |

| <ul> <li>Integration manual</li> </ul>                        | <ul><li>Support</li></ul>                     |                                                                  |                                               |  |

| <ul> <li>Software manual</li> </ul>                           |                                               |                                                                  |                                               |  |

| Features                                                      |                                               |                                                                  |                                               |  |

| ◆ High Performance 32-bit RISC-V CPU                          |                                               | <ul> <li>Set-associative caches with data snooping</li> </ul>    |                                               |  |

| <ul> <li>Proprietary 6-stage pipeline</li> </ul>              |                                               | and parity and ECC                                               |                                               |  |

| <ul> <li>RV32GCX instruction set</li> </ul>                   |                                               | Power-down mode                                                  |                                               |  |

| <ul> <li>Variable delayed dual-core lockstep</li> </ul>       |                                               | <ul> <li>On-chip debug support</li> </ul>                        |                                               |  |

| operation                                                     |                                               | <ul> <li>Separate or joint Instruction/Data interface</li> </ul> |                                               |  |

| <ul> <li>Split dual-core mode for high-performance</li> </ul> |                                               | <ul> <li>JTAG and UART Debug Link</li> </ul>                     |                                               |  |

| operation                                                     |                                               | <ul> <li>Free GNU-Based C/GDB toolchain</li> </ul>               |                                               |  |

| <ul> <li>Up to 1.32 DMIPS/MHz/Core</li> </ul>                 |                                               | <ul> <li>Cycle accurate simulator</li> </ul>                     |                                               |  |

| <ul> <li>Up to 2.26 CoreMark/MHz/Core</li> </ul>              |                                               | <ul> <li>Technology independent IP Core</li> </ul>               |                                               |  |

| <ul> <li>Custom instruction set extension</li> </ul>          |                                               | <ul><li>Flexible</li></ul>                                       | <ul> <li>Flexible licensing scheme</li> </ul> |  |

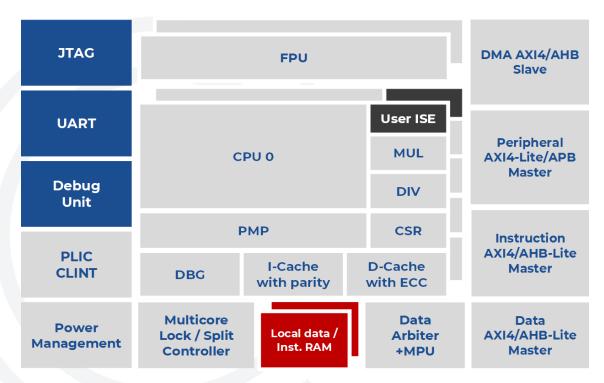

Figure 1. Simplified block diagram.